- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

�FIFO� Recovery� Logic�

�Byte-Controlled� Transfers�

�CorePCIF� supports� both� write-� and� read-controlled� byte� transfers� to� the� backend.� When� data� is� written� to� the� backend,�

�four� (eight� for� 64-bit� operations)� write� strobes� (WR_BE_NOW)� are� provided,� indicating� which� bytes� should� be�

�written.�

�When� data� is� read� from� the� backend� interface,� the� BYTE_ENN� and� BYTE_VALN� signals� can� be� used� to� control� the�

�byte� reads.� The� backend� should� wait� until� BYTE_VALN� is� active� (LOW)� and� then� use� the� four� (eight� for� 64-bit)�

�BYTE_ENN� signals� (active� low)� to� control� the� data� read.� Using� the� BYTE_VALN� signal� prevents� the� core� from�

�bursting� data� every� clock� cycle;� in� that� case,� data� will� be� transferred� once� every� four� clock� cycles� at� best.�

�Dataflow� Control�

�CorePCIF� allows� the� backend� to� stop� data� transfers� in� Master� and� Target� mode,� and� to� initiate� transfers� in� Master�

�mode.� In� Target� mode,� the� BUSY� signal� can� be� used� to� terminate� a� data� transfer� so� it� will� be� retried.� The� ERROR� signal�

�can� be� used� to� simply� terminate� a� transfer.�

�Likewise,� in� Master� mode,� the� STOP_MASTER� signal� can� be� used� to� terminate� a� data� transfer.� The�

�WR_BUSY_MASTER� and� RD_BUSY_MASTER� signals� can� be� used� to� delay� a� DMA� transfer� from� starting.� If�

�STOP_MASTER� and� RD_BUSY_MASTER� are� connected� to� a� FIFO� empty� signal,� the� DMA� engine� will�

�automatically� stop� a� DMA� cycle� when� the� FIFO� becomes� empty� and� restart� it� when� the� FIFO� becomes� non-empty.�

�This� allows� the� core� to� move� data� from� a� FIFO� to� PCI� memory� without� any� host� intervention.�

�FIFO� Recovery� Logic�

�The� CorePCIF� backend� interface� directly� supports� the� connection� of� external� FIFOs� using� internal� FPGA� FIFO�

�memories� or� external� FIFO� devices.� To� prevent� data� loss,� CorePCIF� includes� optional� FIFO� recovery� logic� for� each�

�BAR.� In� normal� burst� operations,� the� core� reads� data� from� the� backend� at� the� same� time� as� previous� data� is� being�

�transferred� on� the� PCI� bus.� When� the� Master� terminates� the� Target� transfer,� it� is� likely� that� data� has� been� read� from� the�

�FIFO� and� not� transferred� on� the� PCI� bus� (� Figure� 6-5� on� page� 56� ).� Without� recovery� logic,� this� data� would� be� lost;�

�however,� if� the� FIFO� recovery� logic� is� enabled� (� Figure� 6-14� on� page� 63� ),� the� core� stores� this� data� until� the� next� Target�

�access� to� the� same� BAR.� Data� loss� also� potentially� occurs� when� the� core� is� operating� in� Master� mode.� In� this� case,� the�

�core� also� needs� to� recover� data� lost� due� to� PCI� cycles� that� are� terminated� with� a� disconnect� without� data� cycle.�

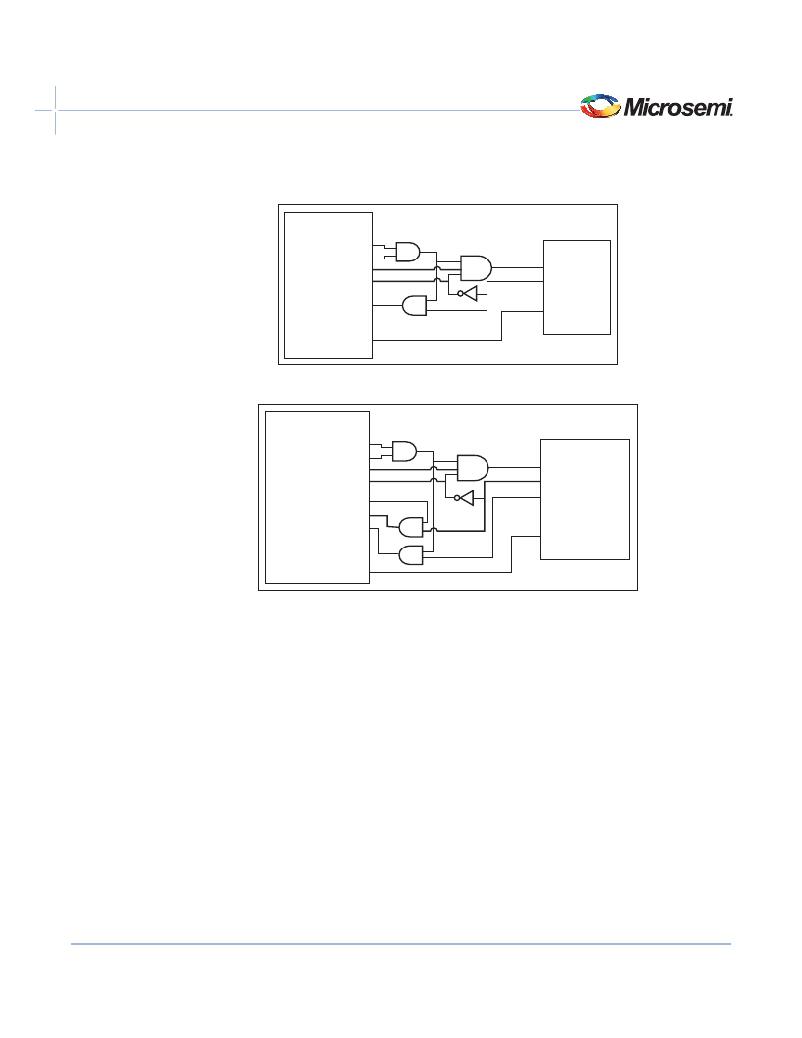

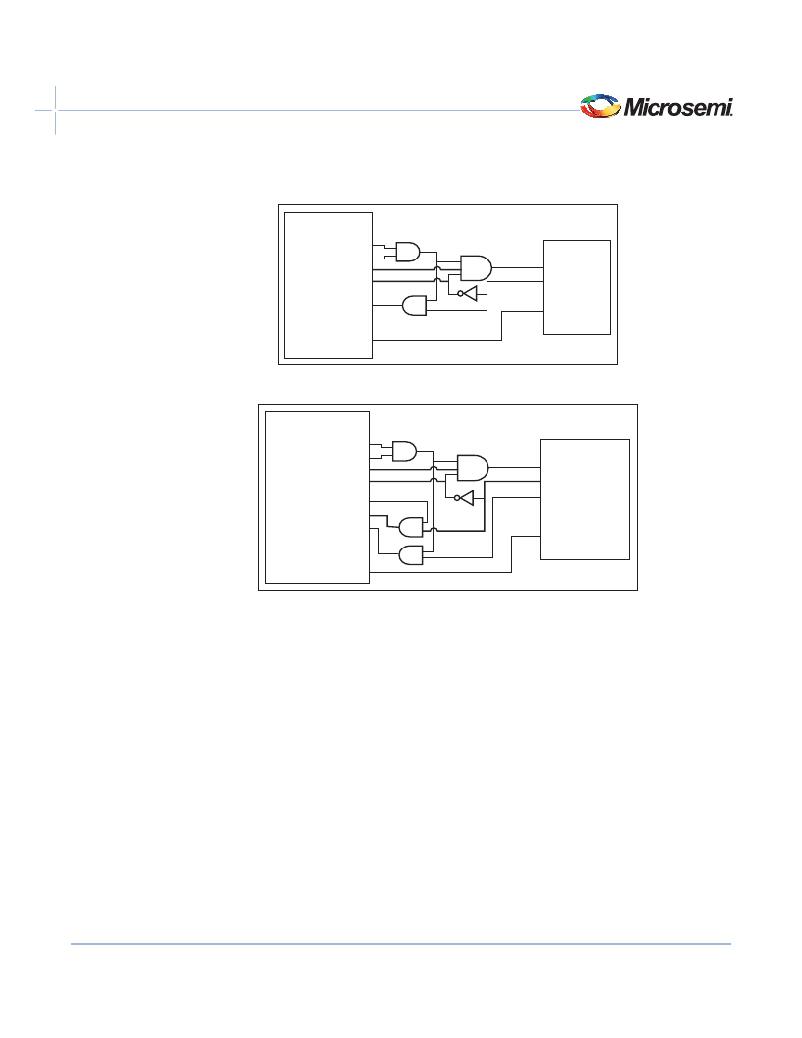

�Figure� 1-2� on� page� 22� and� Figure� 1-3� on� page� 22� show� how� to� connect� a� FIFO� to� the� backend� interface,� supporting�

�Target� and� Master� transfers.� In� Target� mode,� the� FIFO� empty� signal� is� used� to� assert� the� BUSY� input� while� the� FIFO� is�

�empty� and� to� assert� RD_STB_IN� when� data� is� available.�

�In� Master� mode,� the� FIFO� empty� signal� is� used� to� assert� the� RD_BUSY_MASTER� input� while� the� FIFO� is� empty,�

�preventing� a� DMA� cycle� from� starting,� and� to� assert� RD_STB_IN� when� data� is� available.� The� FIFO� almost� empty�

�signal� is� used� to� assert� STOP_MASTER,� which� will� cause� the� current� DMA� cycle� to� be� terminated� as� soon� as� possible.�

�Additional� data� words� may� be� read� from� the� backend� after� STOP_MASTER� has� been� asserted.�

�v4.0�

�21�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: